简介

Layerscape LA1224 系列是一款创新型、高度集成的基带处理器(baseband processor),适用于开放、灵活、可编程的无线通信与信号处理应用场景。支持 5G、卫星通信以及其他各类无线连接。

NXP 为该系列芯片开发了创新的、可编程的向量信号处理加速引擎(VSPA),可扩展性强,总性能可达 1.3 TFLOPS/s(浮点运算能力)。

其特点包括:

可在功耗与性能之间灵活权衡,适应不同应用场景

支持多种数据类型并行处理,提高通用性

支持算法与仿真平台协同开发,简化算法开发流程

芯片还集成了高性能、可配置的 FEC 加速器,支持:

前向纠错(FEC)

混合自动重传(HARQ)

扰码(Scrambling)

循环冗余校验(CRC)

芯片内还包含 6 个通用 RISC 控制器(e200 架构),用于协议控制与帧时序调度等任务。

该系列芯片还提供:

最多两个 PCIe Gen3 控制器

支持最多8条 SerDes 高速串行通道

这些接口主要用于将 LA12xx 芯片与 NXP Layerscape ARM 多核 SoC 搭配,实现主控+协处理架构。

芯片内集成 两个数据转换子系统(DCS),用于与模拟前端(如 CPE、小基站、RU 或雷达设备)通信,包括:

ADC(模数转换)/ DAC(数模转换)模块

支持 Sub-6GHz 和毫米波频段的信号输入输出

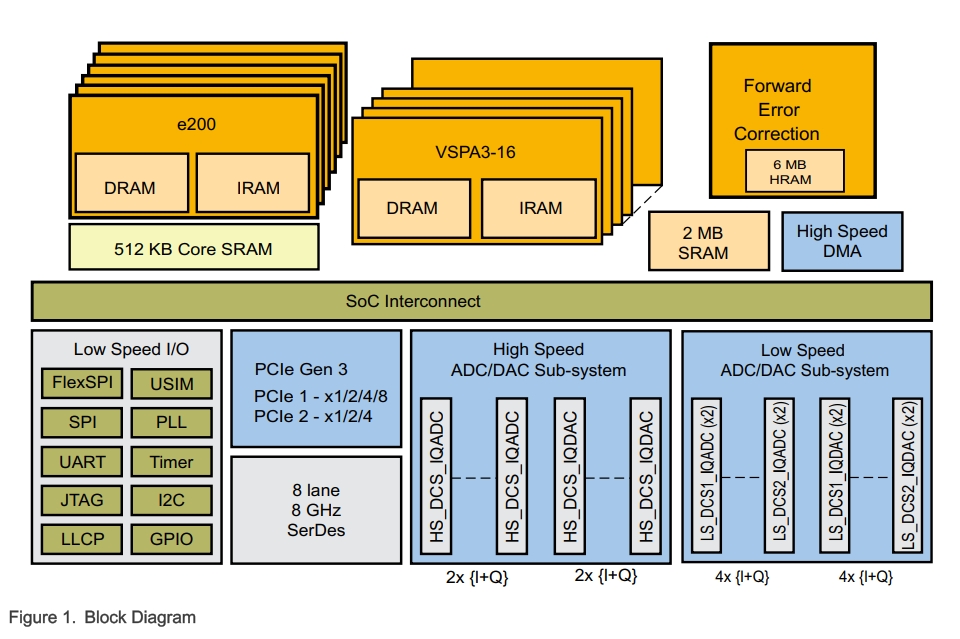

芯片架构

芯片整体架构如下:

1. 通用计算和系统管理功能

- 6 个 e200 Power 架构核心模块,每个模块包括:

- z7260n3 CPU:主频最高 614.4 MHz

- 64 KB 本地数据内存(Local Data Memory)

- 16 KB 指令缓存

- 16 KB 数据缓存

- 64 KB 共享 SRAM

- 512 KB 核心 SRAM

- 2 MB 片上 SRAM

- Multi-banked 实现,提高并发访问效率;

- 同时支持程序和数据访问

- 多处理器中断控制器(MPIC)

- 支持 112 个内部中断 和 12 个外部中断

- 支持核心间通信机制:

- Inter-processor doorbells:核心间的轻量通知机制

- Shared message-signaled interrupts:类似 PCIe/MSI 的中断通信机制

2. DMA

- 芯片内置qDMA(Queue Direct Memory Access)控制器:一种高性能、可配置、面向多通道/多任务的DMA引擎,用于在不同内存区域之间搬移数据,而不需要CPU介入

3. Network-On-Chip interconnect (NoC)

- 提供芯片内部模块之间的 高速、低延迟通信网络;

- 非一致性(Non-coherent):不支持自动缓存同步机制,适用于大吞吐、高效率、显式管理数据一致性的任务,如 PHY 信号流处理。

4. PHY 子系统架构

最多8个 VSPA3 16SP 核心(VSPA-0~7),主频最高 614.4 MHz:

- 16个算术单元(Arithmetic Units, AUs)(支持单精度浮点)

- 或可配置为 32个半精度 AU

- 一个特殊算术单元(SAU),用于复杂或定制运算(如矢量乘积、Log运算等)

- 专用程序与数据存储:

- 128 KB VCPU程序存储器

- 16 KB IPPU程序存储器

- 128 KB VCPU数据存储器

- 192 KB IPPU数据存储器

- DMA用于高效搬运样本数据以及程序Overlay(动态加载)

前向纠错单元(FECU)

- 5G Polar 编码器(0.6 Gbps) / 解码器(2.5 Gbps)

- 支持所有 K/N/E 配置:K=信息位数,N=码字长度,E=比特映射输出

- LDPC 编码器(13 Gbps) / 解码器(9 Gbps)

- 支持所有 K/N/E 组合,兼容 5G 规范

- 支持 早期终止(Early Termination) 提高效率

- 5G Polar 编码器(0.6 Gbps) / 解码器(2.5 Gbps)

文档信息

- 本文作者:Ziyue Qi

- 本文链接:https://www.qiziyue.cn/2025/07/16/NXP-1224%E6%A6%82%E8%BF%B0/

- 版权声明:自由转载-非商用-非衍生-保持署名(创意共享3.0许可证)